## Zynq platform and related instruments

Peter Leban, DEELS, June 2017, Paris

# Content

Peter's project (continuation)

Company's projects (continuation)

#### LAST YEAR'S CONCLUSION

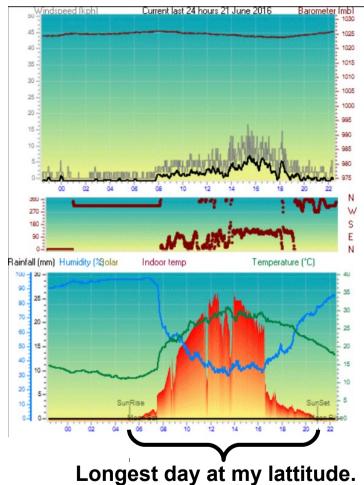

# Step 4. This was my project

http://freeweb.t-2.net/vreme tmin

# Step 5. Time for improvement

### vremetolmin.si

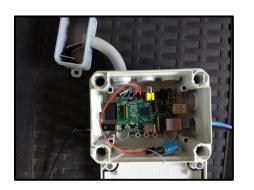

### Hardware upgrade:

- 2.5-second wind sampling

- Standalone unit (no wood housing required)

- Standalone solar sensor

- Soil temperature sensors

- Night cloud sensors

- Lightning strike detector

# Latest performance

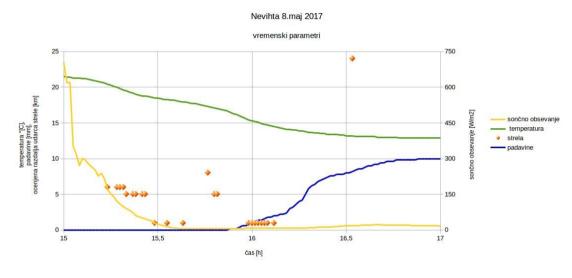

#### Below: A short and weak storm

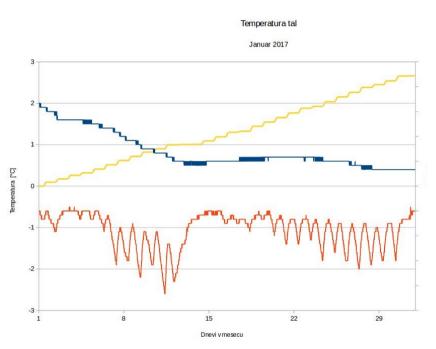

Above: January 2017 soil temp & sun Below: Live data (2-second update)

017-05-24: udarci strel cez dan Stevilo udarcev v uri Cas[h]

Right: A stormy afternoon & night in vicinity

#### Last year's presentation:

### present and future platforms with Zynq SoC

- Faster sampling rate: bunch-by-bunch BPM, cavity BPM, Beam loss monitor

- Optical links

- More input channels

- *Analog output(s)*

- More I/O interfaces (digital)

- Exchangeable front-end

- Better long-term stability performance

Which requirements did we fulfill and what did we develop since 1 year ago?

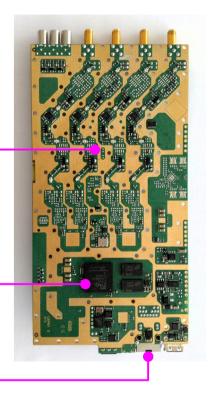

# Platform C (or 'Zynq 7020' platform)

Zynq 7020

3x Input / output LEMO:

Max what this PCB supports

4 channels with various assembly options:

Easier than having exchangeable version

Zynq 7020

PoE

2x dual channel ADC:

Still 125 MHz

Extension slot

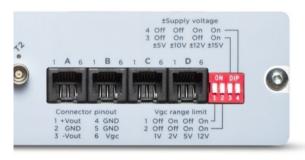

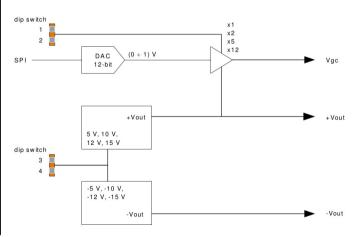

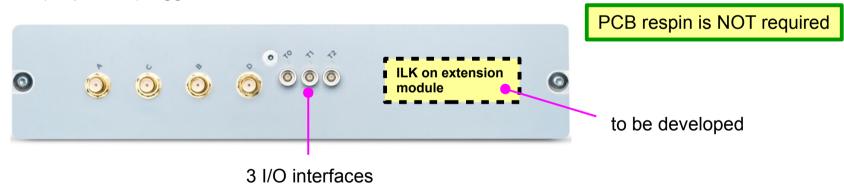

### Platform C extension modules – BLD connections

### Zynq 7020

- 4x RJ25 interface

- DIP switch

- Power supply and gain control for the PMTs

- Direct control from Zynq (FPGA and OS)

### Platform C extension modules – beamline feedback

### Zynq 7020

Extension module still to be specified; possible options:

- Analog interface (e.g. SMA)

- Digital interface (e.g. RJ-11, RJ-25, RJ-45)

- DAC & protocol have to be specified

# Platform C extension – GbE output

#### Zynq 7020

It is available in Libera Photon. The PCB is slightly different from the BLM, Spark and Digit

#### RJ-45 for fast data output (UDP)

#### Available options:

- TBT streaming data (depends on the data rate)

- FA streaming data

- Other continuous data stream, processed by the FPGA

Availability foreseen Q4 2017

PCB respin required

# Platform C extension – ADC sensitivity

Zynq 7020

It is configured during assembly. For the future, it could be done runtime by user.

#### Available options:

- 0.5 V full scale

- 1.0 V full scale

PCB respin required

Availability foreseen Q4 2017

### Platform C extension – Interlock

#### Zynq 7020

#### Typical use (all configured as inputs)

- T0 ... reference clock (»tbt«)

- T1 ... postmortem trigger

- T2 ... (acquisition) trigger

#### Interlock output on the extension module

- Interlock functionality implementation (FPGA, software)

- Use same circuit as on the Libera Electron / Brilliance / +

**Discussion with Cornell Laboratory**

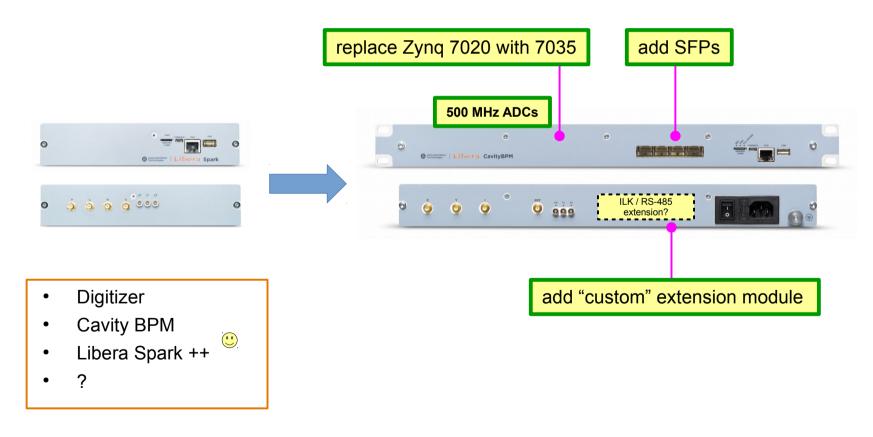

# Faster sampling rate – Libera Cavity BPM

Zynq 7035

#### Last year a render only, this year a working instrument

- Delivered to INFN (Italy)

- Delivered to SACLA (Japan)

- Zynq 7035

- 500 MHz, 14-bit ADCs

- PoE++ (tested), uses 100-240 V

- 6.6 Gbps SFPs supported (with speed grade 1)

#### Available options:

- Add 4 SFP transceivers

- Higher speed grade for 10 Gbps SFPs

- 8 GB memory for raw ADC data storage

- Remove 'cavity BPM' specific front-end digitizer only

www.i-tech.si

Availability not known yet but can be soon

# Zynq 7035 platform – what is next?

Zynq 7035

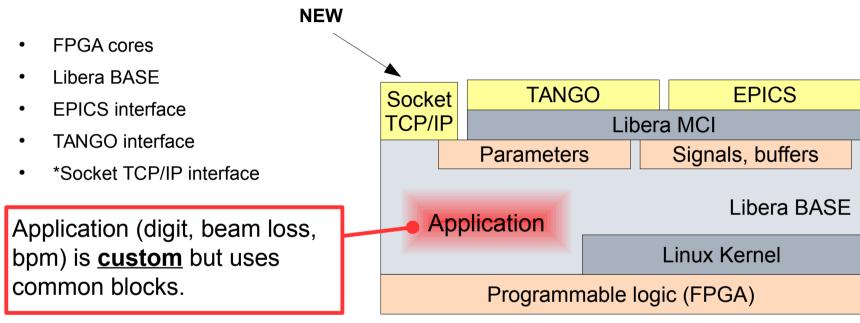

# Software updates

<sup>\*</sup> Development version available only

### What **has not** been done

- Evaluation of the thermally stabilized Libera Spark

- Instrument with more digital I/O and analog channels (no project behind this)

- Ultrascale FPGAs not evaluated yet

- Exchangeable front-end

### What **has** been done

- Offer a digitizer with several (simple) processing options

- Developed a 500 MHz ADC instrument (Cavity BPM)

- New functionalities to Libera BLM, Libera Spark ERXR

- Updated Libera BASE with backward compatible clients

- Several fixes to TANGO interface (thanks to ESRF, SOLEIL)

- Major update to EPICS interface (requested by APS, NSRRC, NSRL)

- GUIs for all instruments; EDM & caQtDM

- VirtualBox image with MCI examples (C++)

### Conclusion

- More instruments & applications have joined Libera

- Keep working with you:

- faster development cycles than before

- cooperate on code (especially the upper layer)

- to understand use cases

- Build new instruments